_____________________

This project was completed while studying at the Korea Advanced Institute of Science and Technology (KAIST) and the aim was to design and implement a RISC-V CPU in Verilog that was both pipelined and had a single-tier cache.

_____________________

The goal of this project was to create a design from scratch that was synthesizable and passed implementation without timing issues, and also to gain more experience in RTL design and testing.

_____________________

This project was entirely executed by myself, with supervision and assistance from KAIST faculty.

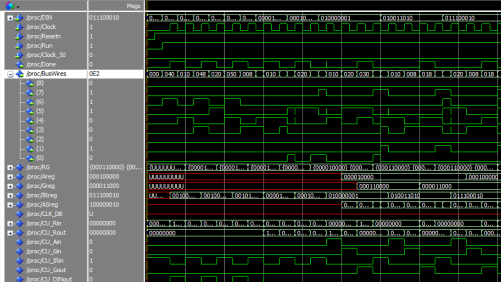

The project result in a successful Verilog implementation of a 32-bit RISC-V CPU with a single-tier cache. It is capable of executing ~44 opcodes and can pipeline instructions, utilizing a branch predictor and preventing read-after-write dependencies to maximize performance.