_____________________

This project's aim was to implement a simple RISC-V based CPU in Verilog and run the sythesized design on an Intel MAX10 FPGA.

_____________________

The goal of this project was to further my understanding of microarchitecture, Verilog desing, and RISC-based processors.

_____________________

This project was entirely executed by myself, with supervision and assistance from my university's faculty.

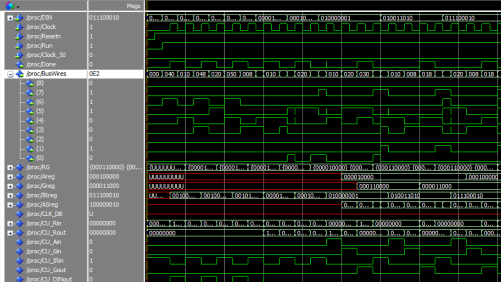

The project result in a successful VHDL implementation of a 9-bit single-cycle CPU with a single-tier cache. It is capable of executing 4 opcodes and has 8 available general purpose registers. Currently, this project is in the processes of being largely expanded into a pipelined Verilog 32-bit CPU capable of supporting over 40 opcodes and with a multi-tiered cache. Additionally, over 10 pages of documentation was produced for this implementation.